成都UFS分析仪那家好

整体功能虽然不能和专业仪器相比,但是用较低的成本来实现特定的功能,也是非常成功的设计。本文以下讨论的逻辑分析仪,主要是指这类入门级设计。基于电脑并口的逻辑分析仪曾是主流,但是近年来电脑系统逐步不再配置并口,这类设计已经成为明日黄花,还具有原理学习的价值。另一类的逻辑分析仪,是以低速单片机为基础的。很多爱好者用PIC、AVR等常见单片机设计了自己的作品。但这类单片机逻辑分析仪的共同弱点就是采样速度太慢,通常不超过1MHz。以USBIO芯片为基础的入门级逻辑分析仪现在为流行。比如Saleaelogic,还有类似的USBee等。这类产品主要采用一个USBIO芯片,例如CYPRESS公司的CY7C68013A-56PVXC,所有的信号触发和处理工作都是电脑上的软件完成的,硬件部分就只是一个数据记录仪。高采样速度为24MHz。它们可以“无限数量”地采样,因为所有的数据都是存储在电脑里的。目前一般多是8个通道,更多的通道数量会成比例地降低高采样速度。这类产品构造简单,方便易用,价格便宜,是调试单片机开发工作的好工具。它的缺点主要是采样速度只有24MHz、8个通道,对于分析高速并行总线就不能胜任了。更进一步的设计,需要增加FPGA、SRAM等器件。DigRF v4协议分析仪/训练器找欧奥!成都UFS分析仪那家好

4、比较帧类型:可自行选择;5、数据:可输入对应帧类型数据的十进制,十六进制,八进制。设置效果如图6所示:图6帧查找属性设置七、解码数据准确定位完成设置,则可以通过查找具体的查找类型进行显示,效果如图7所示:图7查找结果显示此次查找共有68个查找结果,可通过如下操作观测每一个查找结果,效果如图8所示:图8查找结果数据分析ZLG致远电子逻辑分析仪具有超大容量存储、智能过滤存储、高保真不间断实时记录、高效的协议分析平台、触发搜索多样化、灵活的参数测量,能够定位系统运行出错时的特定波形数据。针对数字电路的开发和测试人员可以用逻辑分析仪对电路进行精确的状态或时序分析,以检测分析电路设计中的错误,从而迅速定位,解决问题。黄石PCIE分析仪报价USB PD,3.1, 3.0,2.0协议分析仪/训练器找欧奥!

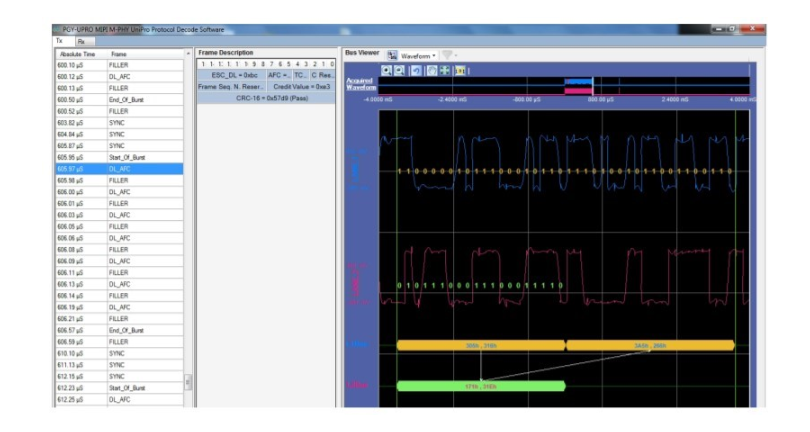

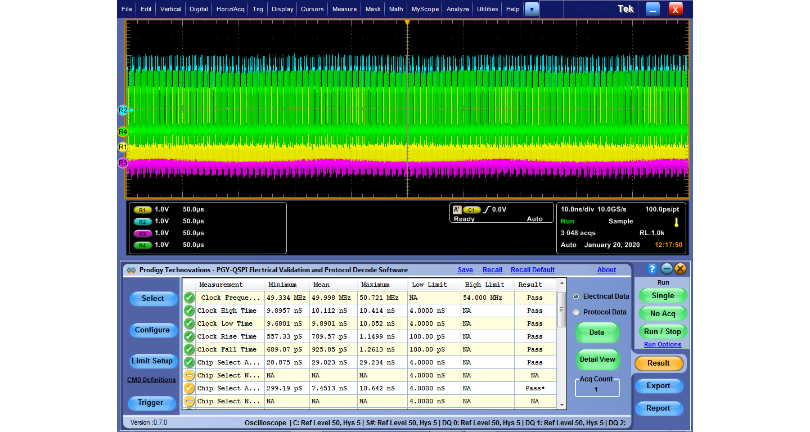

序列步骤存储限定意味着在某个特定的序列步骤内只存储特定的样本。这意味着在使用GoTo(转到)或Trigger。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。触发)操作离开此序列步骤之前。应用该存储限定。如果要为每个序列步骤应用不同的存储限定,该存储限定很有用。例如,可能不希望在ADDR=1000之前存储任何样本,而对于其余的测量,只存储ADDR在1000到2000范围之内的样本。设置序列步骤存储还需要再使用一条分支指令。例如,在查找DATA=005E时,如果只希望存储ADDR在5000到6FFF范围之内的样本,某些情况下可使用以下序列步骤:。这表示“立即存储内存中新获得的样本”。而不表示“从现在起,开始存储”。应当注意。

设置效果如图1所示:图1IIC通道开启三、IIC采样参数设置1、采样模式:同步异步的区别,同步采样优势;2、采样频率:采样频率一般设置为被测信号的4~5倍,需要协议解码的时候需要20倍以上,采样率不够会出现解码错误。被测信号频率高要采用同步采样;3、存储深度:通道复用、分段存储、压缩存储、记录模式(实时存储);4、门限电压:一般设置为1/2(MAX+MIN);5、滤波设置:总线滤波,滤一个采样周期的毛刺信号。通道滤波,滤1~2个采样周期的滤波。总线滤波和通道滤波都是硬件滤波。设置效果如图2所示:图2参数设置四、IIC触发与解码设置1、名称设置为自定义;2、输入总线对应好通道;3、总线设置好地址位。设置效果如图3、图4所示:图3触发设置图4属性配置五、IIC解码分析结果开始采集并存储一段数据,从而进行解析。1、数据段区域,体现了具体数据解析的波形于结果;2、可以通过波形显示设置调节波形观察的方式;3、通过波形缩放能够观察不同时间产生的具体帧传播内容;4、时间表显示区域则会把整个数据段的内容逻辑解析并转化。测试效果如图5所示:图5解码分析六、IIC解码数据查找1、查找总线:IIC;2、开始时间:Ds、A、B;3、结束时间:Dp、A、B。SMI(MDIO)协议分析仪/训练器找欧奥!

图25阻尼电阻探测方式阻尼电阻阻值小的一般规则:目标阻抗的。如果探测环境需要更长的连线,这时候可考虑电阻匹配探测,即在探头尖处附加一个匹配电阻,消除连线的反射。匹配电阻的阻值与连线传输线的阻抗一样即可,但需要考虑信号的衰减。图26电阻匹配探测方式逻辑分析仪的探头主要有3种类型:提前设计型;事后考虑型;定制型。图27逻辑分析仪的探头类型小结:逻辑分析仪探头是逻辑分析仪非常重要的部分,典型探头的形状,连接,参数如下图所示。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器。分析仪/训练器怎么选?找欧奥!黄石PCIE分析仪报价

SDIO协议分析仪/训练器厂家只找欧奥,服务好!成都UFS分析仪那家好

可以在序列步骤内使用布尔逻辑表达式。示例:IfADDR=1000andDATA=2000此表达式意指在同一样本中ADDR必须等于1000且DATA等于2000。欧奥电子是Prodigy在中国区的官方授权合作伙伴,ProdigyMPHY,UniPro,UFS总线协议分析仪测试解决方案不会收到EAR进出口方面的管制。同时还有代理其他总类的协议分析仪,包括嵌入式设备用的SDIO协议分析仪,QSPI协议分析仪及训练器,I3C协议分析仪及训练器,RFFE协议分析仪及训练器等等。我司还有代理SPMI协议分析仪及训练器,车载以太网分析仪,以及各种相关的基于示波器的解码软件和SI测试软件。同时,欧奥电子也有提供高难度焊接,以及高速信号,如UFS,DDR3/DDR4,USBtypeC等高速协议抓取和分析的服务。才能符合此表达式。换句话说。在ADDR等于1000的同时DATA等于2000。因此,如果要在同时发生两个事件时触发,则应使用布尔逻辑表达式。常见错误是应使用布尔逻辑表达式时尝试使用两个序列步骤,或者应使用两个序列步骤时尝试使用布尔逻辑表达式。当多个事件同时发生时使用布尔逻辑表达式,而在一个事件接着一个事件发生时使用多个序列步骤。分支:分支类似于C编程语言中的Switch语句和Basic中的SelectCase语句。分支可提供测试多个sADDR”。成都UFS分析仪那家好

上一篇: 成都PCIE分析仪售价

下一篇: 成都协议分析仪找哪家